ad630简介

AD630是一款高精度平衡调制器,结合了灵活的换流架构,通过激光晶圆调整的薄膜电阻提供精度和温度温度稳定。它的信号处理应用包括平衡调制和解调,同步检波【synchronousdetecTIon】,相位检测,正交检波,相敏检波,锁相放大,和方波乘法。板上应用的电阻网络提供精确的±1,±2闭环增益在0.05%的精度(AD630B)。这些电阻用于精确配置多路器的增益为+1,2,3,4。或者,使用外部反馈,允许设计者实现高增益或者复杂转换的反馈拓扑结构。

AD630能够作为一个精确的运放,有两个差分输入阶和一个精确的比较器(用于选择有源前段acTIvefrontend)。比较器的快速响应时间与电压转换速率【slewrate就是电压转换速率(SlewRate),简写为SR,简称压摆率。其定义是在1微秒或者1纳秒等时间里电压升高的幅度,直观上讲就是方波电压由波谷升到波峰所需时间,单位通常有V/s,V/ms,V/μs和V/ns四种。电压转换速率用示波器就可以测量。】和线性放大器最小转换失真的快速设置想耦合。另外,在-100dB@10kHz,AD630在通道间的串扰极低。

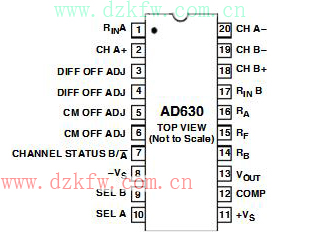

ad630引脚图及功能

AD630的特性

①可从100dB噪声中恢复信号;

②频道带宽:2Mhz;

③压摆率:45V/us;

④串扰:-120dB(1kHz);

⑤引脚可编程、闭环增益:±1和±2;

⑥闭环增益精度和匹配:0.05%;

⑦通道失调电压:100μV(AD630BD);

⑧350kHz全功率带宽。

ad630原理

这个电路可以工作在输入信号频率从DC到几百kHz的范围内。最佳的工作频率范围为 DC 到几kHz。在这个频段,这个电路的效果应该时这些精密整流电路中最好的。上述电路的输入阻抗随输入电压的极性变化,输入电压为正时输入阻抗很高,输入电压为负时,输入阻抗较低。所以对信号源的输出阻抗有一定的要求,如果输入信号的输出阻抗较高,需要增加一级缓冲级。

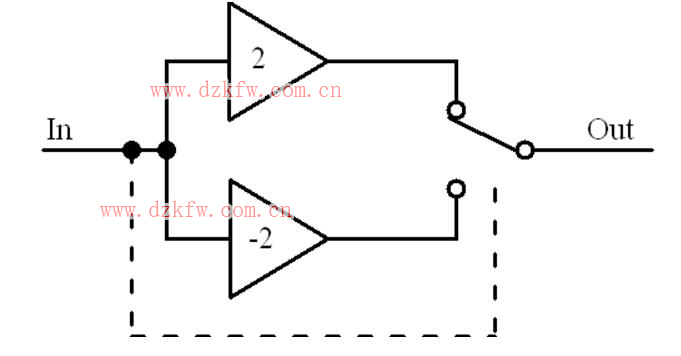

AD630工作原理

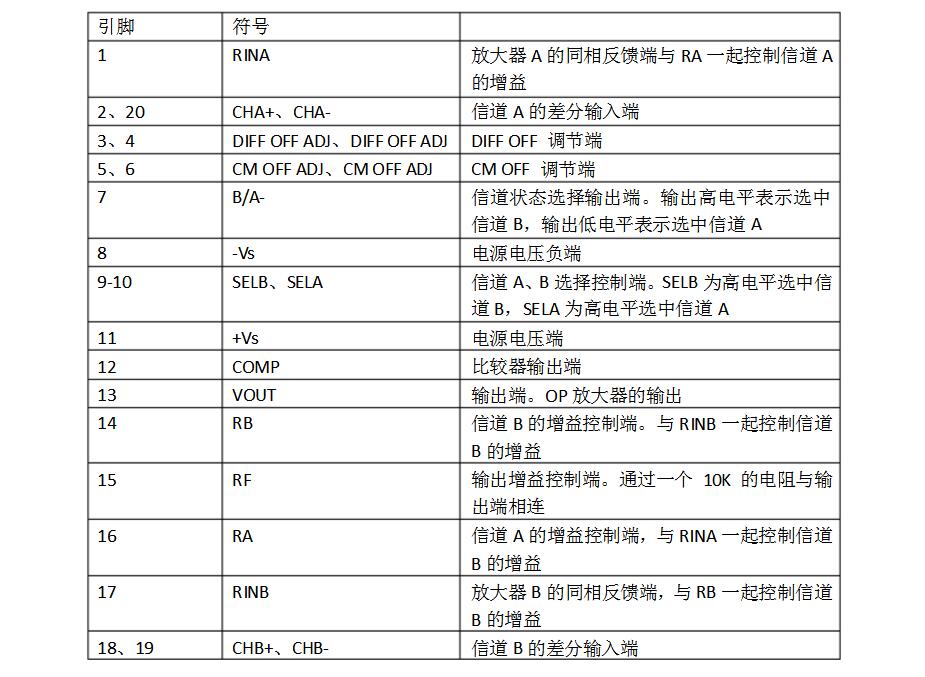

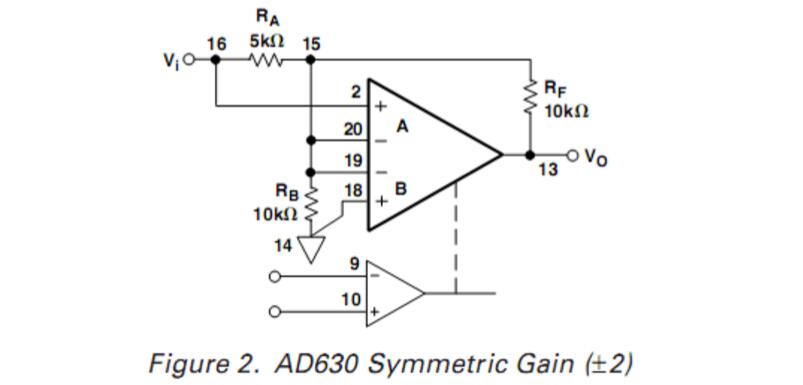

AD630的操作运行方式可能会更容易识别为一个敏感电压比较器的控制下的可以插入到信号路径中的两个固定增益级。当电路在正相和反相增益之间转换,他提供了基本的调制解调功能。630是唯一的包括了激光晶圆调整的薄膜反馈电阻在单片芯片内。在图2中配置产生了±2的增益并且能够容易的通过移动RB从地连接到输出端口转换到±1增益。

比较器选择两个输入级中的一个去完成运行的反馈连接,取消选择输入是关闭的,并且对操作的影响可以忽略。

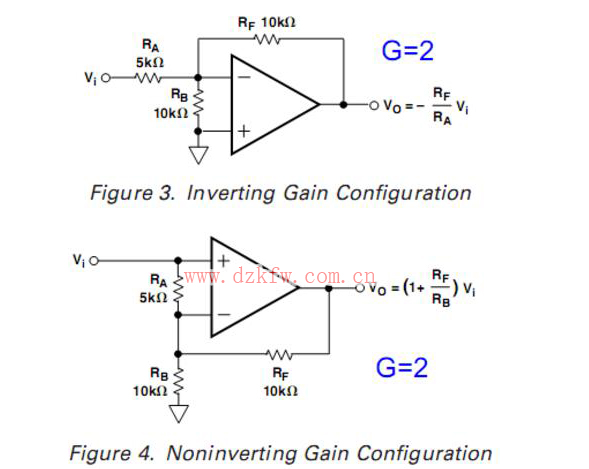

当通道B被选择,电阻Ra和Rf作为反相反馈连接,在如图3的反相增益配置框图。放大器有足够的环路增益来减小Rb在反馈连接的虚地端的负载效应。当比较器的输入符号反转了,输入B取消选择,A被选中,新的等效电路为同相增益配置(如图4)。Ra通过了运放的输入终端,但由于放大器驱动差分电压为0,闭环增益不受影响。

当Rf/Ra=1+Rf/Rb时,这两个闭环增益大小相等,这是由于使Ra等于RfRb/(Rf+Rb),Rf和Rb的并联等效电阻。

5KkΩ和两个10kΩ电阻可以使得AD630的增益为2。通过并联10kΩ的电阻使得Rf等于5kΩ,减去Rb,电路被编程为±1的增益(如9a所示)。这些和其它的,使用芯片上的电阻的配置表述了一个2.5kΩ的源阻抗的反相输入端。更完整的AD630框图表示了在同相输入端2.5kΩ电阻有效,这样能够方便减小由于输入偏置电流导致的误差。

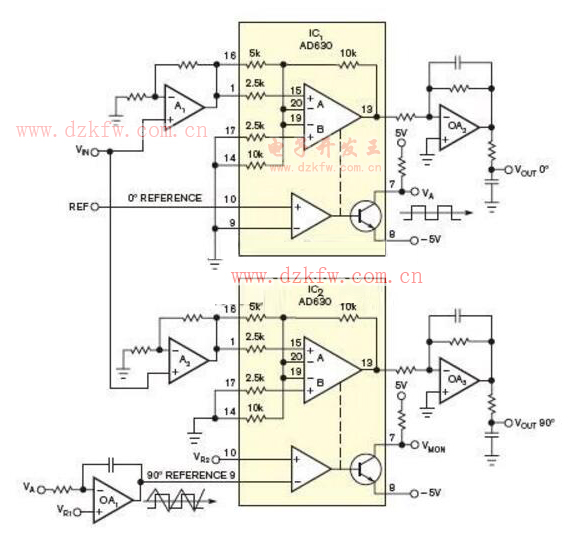

ad630应用电路一

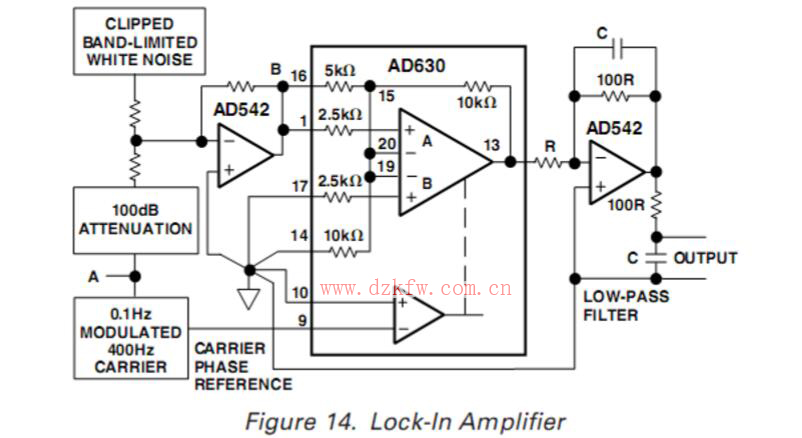

锁定放大是一种从干扰噪音中分离小窄带信号的方法,它充当检测器和窄带滤波器的作用。在有大量不相关噪音的情况下,当期望的信号的频率和相位已知,非常小的信号能被检测出来。

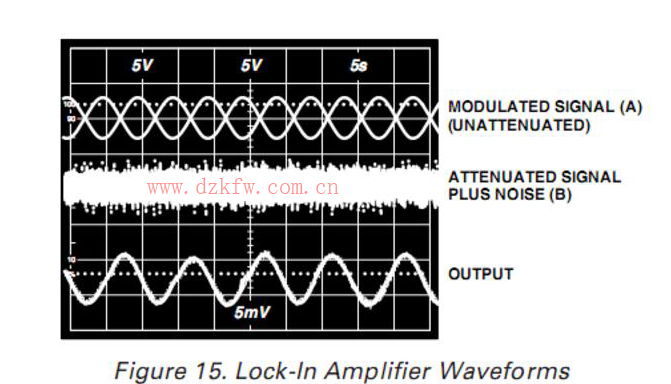

锁定放大器就是一个基本的同步解调器后跟随一个低通滤波器。锁定放大器的应用的一个非常重要的测量参数就是解调器的动态范围,如图14所示的原理图,表示了用于锁定放大器时AD630的动态范围,图15为示波器照片,显示了AD630很大的动态范围。此图演示了一个400Hz的调制信号从大小近似自身100000倍的噪音信号种恢复出来。

测试信号400Hz的载波调制0.1Hz的正弦波产生,正弦调制波形用于清楚的说明,信号通过类似于图9b的电路产生,显示在如图15上部的轨迹。他被衰减10万次,规范化求和放大器的输出B。噪音信号通过求和放大器加入到调制信号中,这个信号是简单的带限裁剪的白噪声。图15的中间轨迹显示了衰减的信号和噪音的叠加。混合信号使用相位信息同步解调(相位信息来自于调制器),结果为使用2极点的简单滤波器进行低通滤波,滤波器对输出端提供100增益,恢复后的信号在图15的下部。

上述这个混合的信号和干扰噪音类似于要求进行检测的锁定放大的信号。AD630精确的输入性能提供了大于100dB的信号范围,并且其动态响应允许其用于载波频率比实例中的大于两个或以上的数量级。一个更复杂的低通输出滤波器,将有助于抵抗更宽的带宽干扰。

ad630应用电路二

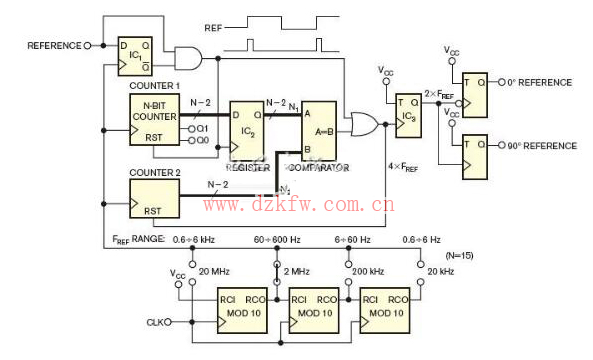

图2描绘了一条全数字电路,你可在小型CPLD中实施该电路,来产生图1中的0和90?基准信号。1号计数器以数字时钟脉冲的数量N的形式来测量基准信号时间,其中的基准时间可能不同于50%。在基准信号的每个正前沿,该计数器在N1=1处收到一条预设命令。D型双稳态多谐振荡器IC1产生这类脉冲。

图1:OA1把双极VA信号积分,并创建三角波。VR1和VR2获得关于VA的90。相移基准电压。

图2:你可在小型CPLD中实现这条全数字电路。

当基准时间超过N/4整数值的大约四倍时,就会缺少最后的EQ信号。为了克服这个问题,RST脉冲和EQ脉冲的“或”组合会在每个基准时间周期内产生四条几乎等距的命令。N/4整数除法是逻辑右移N1的两位,在最后的脉冲位置上产生最大误差3。T型双稳态多谐振荡器IC3产生一个信号,频率为基准信号的两倍。这样,准确度等于3/N1。

为使准确度至少能与AD630相比,1号计数器的N1输出将为最高值。但是,如果你希望N1达到较高值,那么对于给定的数字时钟频率,位数的增加会使最大基准频率下降。

返回顶部

返回顶部 刷新页面

刷新页面 下到页底

下到页底