NE555介绍,时基集成电路

NE555 (Timer IC)为8脚时基集成电路,大约在1971年由Signetics Corporation发布,在当时是唯一非常快速且商业化的Timer IC。NE555体积小、重量轻、稳定可靠,操作电源范围大,输出端的供给电流能力强,计时精确度高,温度稳定度佳,且价格便宜 。555定时器是一种应用极为广泛的中规模集成电路,该电路使用灵活、方便,只需外接少量的阻容原件就可以构成单稳、多谐和施密特触发器。因而广泛用于信号的产生、变换、控制和检测。

1脚:外接电源负极或接地(GND)。

2脚:TR触发输入。

3脚:输出端(OUT或Vo)。

4脚:RD复位端,移步清零且低电平有效,当接低电平时,不管TR、TH输入什么,电路总是输出“0”。要想使电路正常工作,则4脚应与电源相连。

5脚:控制电压端CO(或VC)。若此端外接电压,则可改变内部两个比较器的基准电压,当该端不用时,应将该端串入一只0.01μF电容接地,以防引入干扰。

6脚:TH高触发端(阈值输入)。

7脚:放电端。

8脚:外接电源VCC(VDD)。

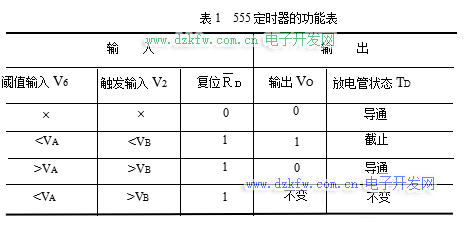

(2)555功能介绍

555定时器的功能主要是由两个比较器C1和C2的工作状况决定的。由图1可知,当V6》VA、V2》VB时,比较器C1的输出VC1=0、比较器C2的输出VC2=1,基本RS触发器被置0,TD导通,同时VO为低电平。

当V6《VA、V2》VB时,VC1=1、VC2=1,触发器的状态保持不变,因而TD和输出的状态也维持不变。

当V6《VA、V2《VB时,VC1=1、VC2=0,故触发器被置1,VO为高电平,同时TD截止。

这样我们就得到了表1 555定时器的功能表。

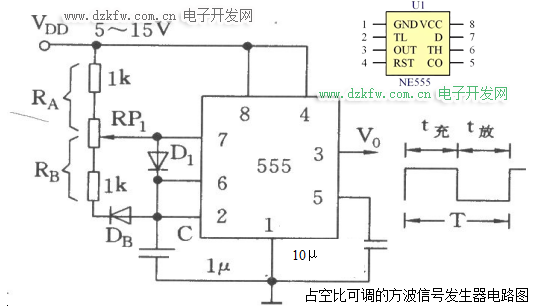

2、占空比可调的方波信号发生器

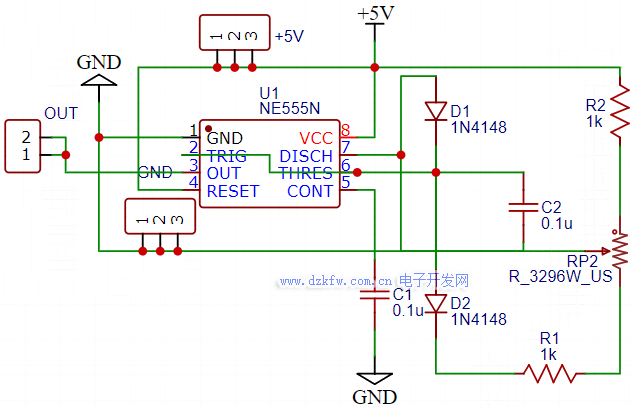

(1)占空比可调的方波信号发生器电路图

图2 利用555定时器设计方波电路原理图

(2)占空比可调的方波信号发生器分析

3、实验数据

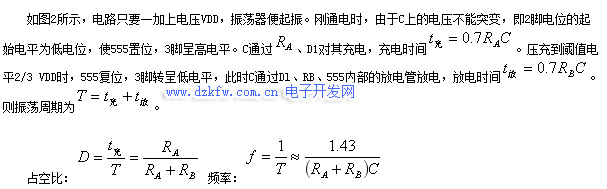

(1)仿真电路图

图3 MulTIsim电路图

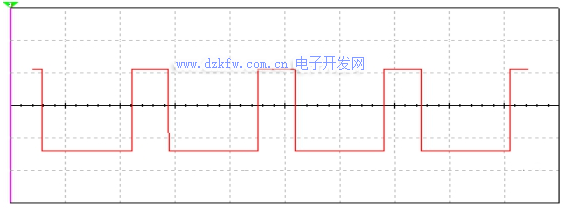

(2)仿真电路结果

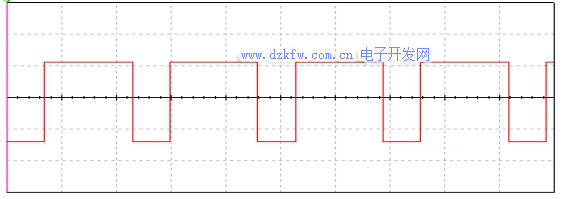

图4 占空比为50%的方波波形

图5 占空比小于50%的方波波形

图6 占空比大于50%的方波波形

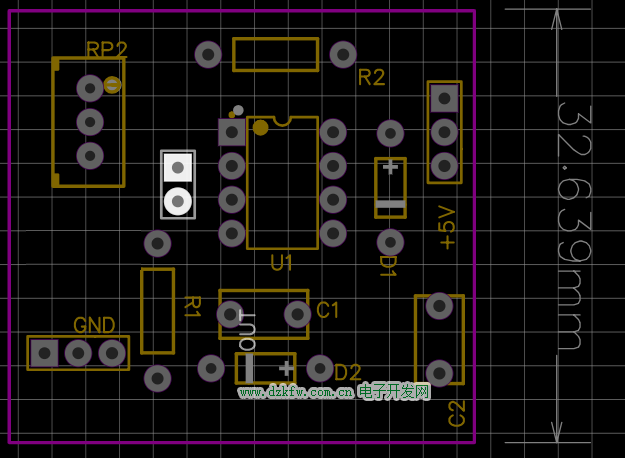

4立创EDA

原理图

PCB原理图

画PCB注意事项:

a.原理图线路不能有交叉;

b.线宽和间距设为0.762,更容易导通信号

c.飞线不能从电容下方走过

d.飞线不能成90°

原由:直角这个位置PCB线的宽度发生了变化(那阻抗就会发生变化),会产生EMI干扰,即电磁干扰。

直角位会产生寄生电容,影响信号质量(影响最大的就是时钟信号的上升时间和下降时间)

1、给电源铺铜可以过更大电流

2、给地铺铜可以减小信号阻抗的作用

3、晶振底下铺铜,防止晶振高速信号对周围信号产生干扰。

4、网格铜(高速信号),实心铜(走大电流)

在NE555三号引脚(输出脚)需要放入排针的目的是为了让示波器观察它

返回顶部

返回顶部 刷新页面

刷新页面 下到页底

下到页底