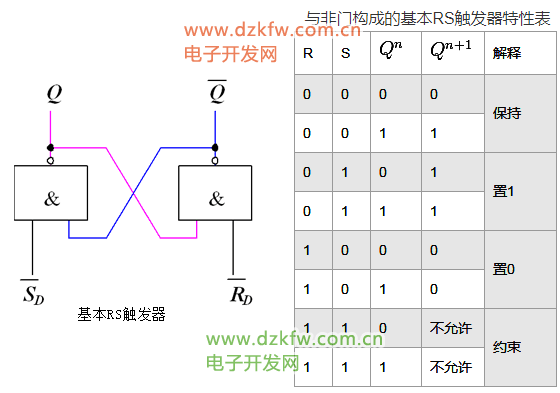

RS����������һ�ֻ�����ʱ���·Ԫ�������ڴ洢һλ��1��0������������������Ż������������ʵ�֡��ڻ����ʵ�ֵ�����£�RS�������ĵ�·�ṹ���£�

- ��·��ɣ�RS�������������������ɣ����������R��S�ֱ����Reset������λ����Set������λ���������Q��������������״̬����Q�Ǵ�����Q��״̬��

- �����ܣ�

��R=1��S=1ʱ������������ԭ����״̬���䣬��Q=Q�ǡ�

��R=0��S=1ʱ��������Ϊ0̬��Q=0��Q��=1��

��R=1��S=0ʱ��������Ϊ1̬��Q=1��Q��=0��

��R=0��S=0ʱ����������״̬���������ܻ����Q��Q��ͬʱΪ1��ͬʱΪ0����������Dz������ġ� - �����ţ�

����RS������������������������ŵ����������˽���������ɣ�����R��S�ֱ������λ����λ��

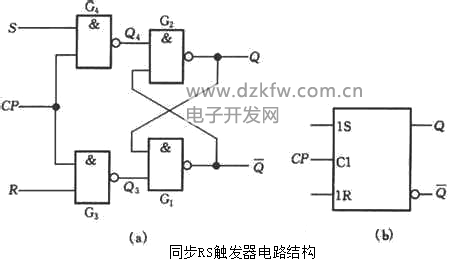

- ͬ��RS��������

ͬ��RS����������������RS�������Ϳ����Ŧ���ɣ����п�����G3����G4��������ʱ������CP=1ʱ���������G1��G2��ʹ���Q����ԭ����״̬���䡣

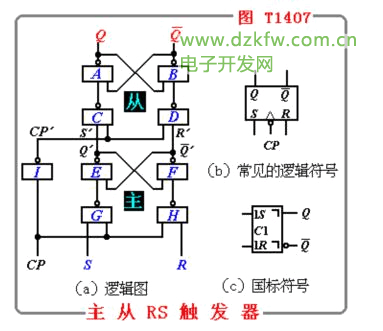

- ����RS��������

����RS������������ͬ����������һ������������ɣ��������������������Ϊ�Ӵ����������롣��CP=1ʱ�����������������������R��S���ź�״̬������

���ض���

���ض��� ˢ��ҳ��

ˢ��ҳ�� �µ�ҳ��

�µ�ҳ��