PART�C 0 ����֪ʶ

�ڽ�MOS��֮ǰ������������һ�°뵼����ϡ�����ͼ��

���ʼǣ�

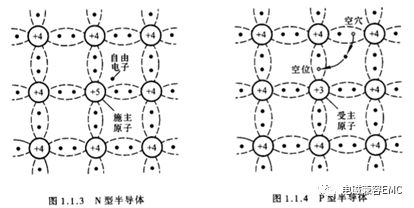

N�Ͱ뵼������ΪPԭ�ӣ�����Ϊ����

P�Ͱ뵼������ΪBԭ�ӣ�����Ϊ��Ѩ

�������ʰ뵼�����п������ƶ��Ķ��ӣ���N�Ͱ뵼���P�Ͱ뵼����Ӵ������ӷ�����ɢ�˶������ɵ��������ɿ�Ѩ�����γɿռ�������Ҳ�������dz�˵�ĺľ��㡣

�������ʼǣ��ľ�����û�������ƶ��ĵ������ӡ�

PN��Ľ���ݵij����̣�ʵ���Ͽ��Խ��Ƶؿ����Ժľ��㸴�ϵ����ɴ������ӽ��в��䡣

��ӵ�ѹ��

��PN�������ƫ��ѹ����PN�������������ĵ�ѹʱ���ľ��㵼�����Ӳ�����ϣ����Ը��������ʰ뵼��һ���߱�������������·��ͨ��

�෴�ģ����PN����ӷ�ƫ��ѹ���ľ�������·��ֹ��

PART-1 MOS�ܽṹ

���Ŀ�ʼ����MOS�ܣ�����ǿ��N-MOSFETΪ���ӽ��н��⡣

��ǿ��N-MOSFET��ȫ�ƣ�N������ǿ�;�Եդ��ЧӦ�ܣ��ڽ�����ṹǰ�������ס�����ؼ��ʣ�

�� N����

�� ��Եդ

�� ��ǿ��

�� �������

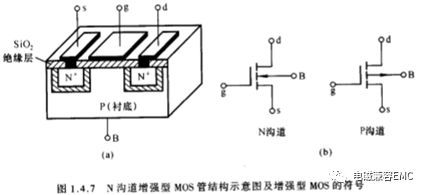

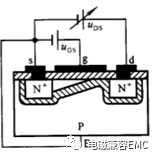

��ģ���飨ͯʫ�ף����İ棩��������Ϥ�Ľṹʾ��ͼ��ʾ��N������ǿ��MOSFET�Ľṹ����Ϊ��

��P�Ͱ뵼��ĵ��ϣ���������N�Ͱ뵼�����������������缫����ΪԴ��S��©��D������P�ĵ�������һ��SiO2��Ե�㣬������һ�������缫��Ϊդ��G��

��ṹ�����ɽ���Ϊ���¼��㣺

������N�Ͱ뵼��ֱ�Ӽ���P�Ͱ뵼��ĵ��ϣ�����N����P��֮����γɺľ��㡣

������դ��G�Ǽ���SiO2��Ե���ϣ���P�Ͱ뵼��ĵ䲢�����磬ֻ�е糡����

��դ��G��ӵ糡������P�Ͱ뵼���е����ɵ��ӣ�ͬʱ���ľ��㣬�γɷ��Ͳ㵼�繵������������N�Ͱ뵼������ʹ����ǿ��N-MOSFET��ͨ��

�� ����������N-MOSFETʱ����Դ��S��P�Ͱ뵼��ĵ�ֱ�����ӣ�Դ��S��ͬ��P�Ͱ뵼��ĵף���©��D��N�Ͱ뵼����֮����һ��PN�ᣬ��PN�ἴΪN-MOSFET��������ܡ�

������ͼ��ʾ����ǿ��N-MOSFET���缫֮�����һ���������ݣ�����Դ��S��©��D֮��ĵ���CdsΪ��������ݣ��ṹ��Ϊ�������λ��PN��Ľ���ݣ�դ��G��S����D��֮��ļ�������Cgd��Cgs֮��Ϊ������ݣ�ʵ����Ϊ�γɷ��Ͳ�������ĵ��ӣ�����Ϊ�η�Ϊ�������ݣ����Ľ���MOS�ܿ��ع��̵�ʱ��������ͣ���

PART-2 MOS�ܵ�ͨ����

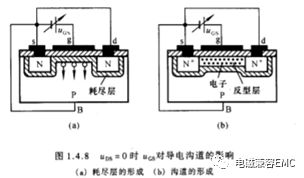

MOS�ܵĵ�ͨ���̣���ʵ�����γɷ��Ͳ㵼�繵���Ĺ��̡�

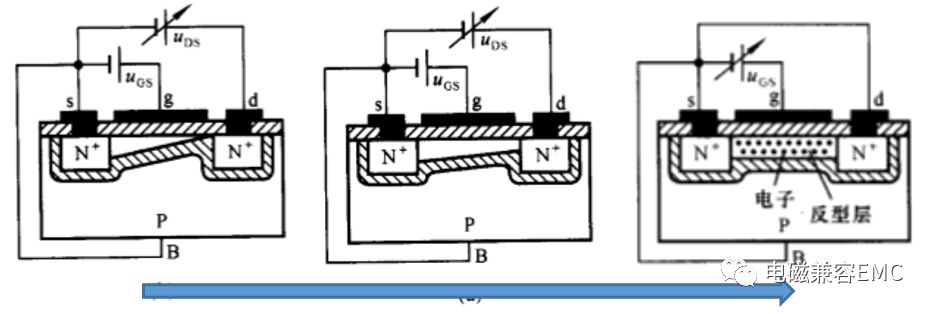

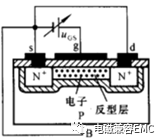

���¿�������ͼ����դ��G��Դ��S֮���һ����ƫ��ѹVgsʱ����ǿ��N-MOSFET��P�Ͱ뵼��ĵ��еĵ����ܵ糡���ã��ᱻ������դ��������ͬʱ��������N�Ͱ뵼�������γɷ��Ͳ㵼�繵����

���úڰ壡���ص㣡

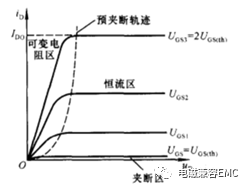

���繵���ո��γɵ�ʱ���Ǹ���ƫ��ѹVgs����Ϊ������ѹVgs��th�������Ϊ����ֵ��ѹ������Vgs����Vgs��th������һ�ε�ѹ���䣬��Ϊ�ɱ��������MOS��©��D��Դ��S�ĵ�ͨ�迹��Vgs��������ͣ���Vgs����2��Vgs��th��֮������Ϊ��ͨ�迹Rds-on��Ϊ��ͣ�s�����¶�һ��ʱ���ֲ��䣬��ʱ��ǿ��N-MOSFET��Ϊ��ȫ��ͨ������ͼ

�����ÿ���MOS��������ѹʱ��һ������ΪԶ����2��Vgs��th����

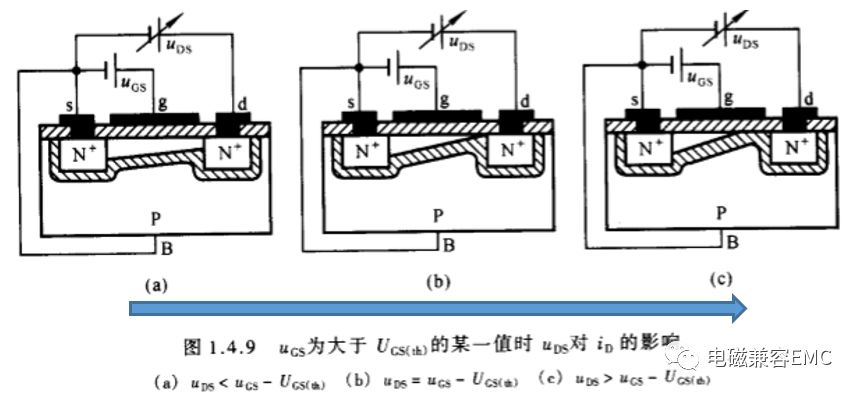

ģ�����и�����ôһ��ͼ�������˵�Vgs���ڿ�����ѹʱ��Vds�������������MOS�ܵĵ���iD��Ӱ�졣

ʵ���Ͻ�ͼ���������Խ��Ƶ�ģ��MOS�ܿ������̷��Ͳ���г̹��̣�

MOS�ܵ�����̿ɽ�������Ϊ��

�����ڵ糡���ã����γɿ���Դ��S����ķ��Ͳ㣬ʹ��MOS��©��D��Դ��S֮����Ե�ͨ����������iD��

��iD��ʼ������ͬʱ�����Ͳ�����©��D��������ʹ�ÿ���©��D�ķ��Ͳ��뿿��Դ��S�ķ��Ͳ���Ȼ���һ�¡�

�۷��Ͳ��������Rds-onһֱ������ȫ��ͨ�����ֲ��䡣

��Cgd���Ĺ��̣�Vgs���ֲ��䣬��ʱRds-on�ϴ���������iDһ��ʱ��MOS����Ľϴ�

��դ��G��ӵ�ѹ��MOS�ܵ�ͨ���̣�Vgs���ֲ���������Ϊ�������䣬���ڷ��Ͳ���γɹ��̶�Ӱ���Vgs��Rds-on��MOS����ı仯���̵������Ϊ����ЧӦ�������ϲ�����ϸ����һ������ЧӦ��

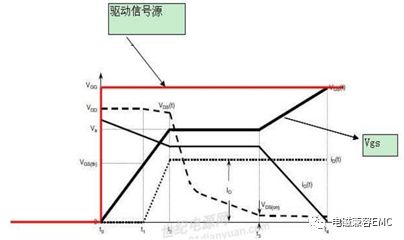

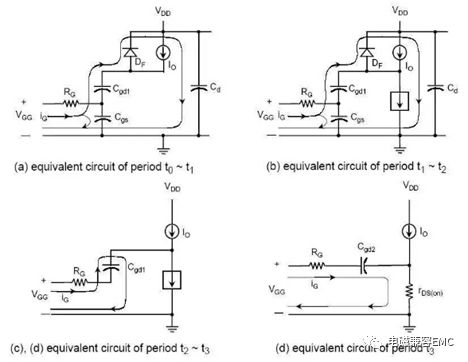

��������̳��һ�����ͽص�һ��ͼ���Ѿ�����������������դ�������Ժ�ʱ��MOS����ص�����ѹ�ı仯�����

�����ײ�ԭ�����ӣ�

t0-t1������դ����ѹδ���↑����ѹ��MOS��δ��ͨ������ͼ

t1-t2�� Vgs�����˿�����ѹ��MOS�ܿ�ʼ��ͨ�����Ͳ㲻���ؿ���դ����ѹ�������ߣ�����ͼ��

t2-t3�� MOS��λ�ڿɱ�����������ֳ�����ͨ�����Ͳ���©�����ؿ�����������ͼ���������դ����ѹ���䣬��������ƽ̨��

t3-t4�����Ͳ�����ؿ�������һ�µ������դ������ʩ��������ѹ���������Ͳ�һ���ؿ���ֱ��դ����ѹVgs�������ź�Դһ�£���ͨ�迹Rds-on��

��MOS��ģ�Ϳ��Ļ����������²���ͼ��Ҳ�ͽ�����Ϊʲô���Ͳ���������CissҪ������Ϊ��������Cgs��Cgd������Ϊ���ߵij��˳��һ����

PART-3MOS�ܲ���

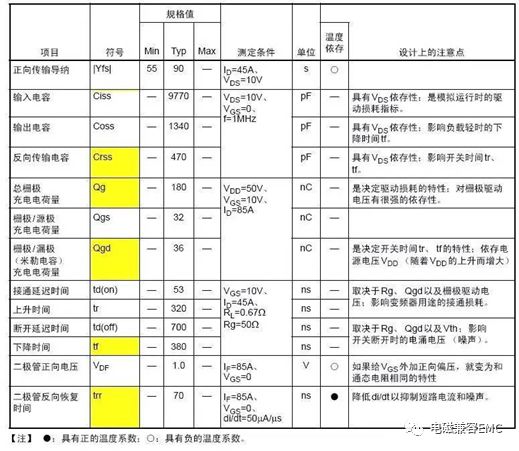

���Ÿ�λ���߶�MOS�ܵIJ����Ѿ����������ˣ�����Ͳ�����ϸ˵���ˣ��������IJ����и����Ľ��ܣ�����������в��ֲ������в���˵����

1��������MOSFET�ľ������ֵ��

ע�٣�©Դ����ѹVDSS������Ϊ����ʩ��������������˵ĵ�ѹֵ����ֻ��һ������

ע�ڣ�դԴ����ѹVGSS����ʩ����դ���缫��Դ���缫֮��ĵ�ѹ������դ����P�Ͱ뵼��ĵ��м���SiO2��Ե�㣬ֻҪ��ѹ����ֵ������Ե����ѹ�������������������������

ע�ۣ�©��������ID��������������ķ���©��������IDR�����ΪIS��һ����������ֵһ�£���Ϊ����N�Ͱ뵼����P�Ͱ뵼��ĵ��γɵ�PN�����������

ע�ܣ�ID��pulse����Ҫ��ʩ�ӵ�����������ȣ�������һ�µIJ������ù�������ݡ�

ע�ݣ�ѩ������IAPͬ����Ҫ��ע������ȡ�

2������̬������

ע�٣�Vgs��off����ʵ���ǿ�����ѹVgs��th����ֻ��������ĽǶȲ�һ����

ע�ڣ�����ǰ�ĵĶ���Ӧ��֪��Ϊʲô��������Rds��on����С�в��죬��֪���Ļ�ȥǰ�����¿���

3������̬������

ע�٣�Ciss = Cgs + Cgd ��Coss = Cds ��Crss = Cgd

ע�ڣ�MOS�ܿ����ٶ�����Ҫ��ע�IJ�����Qg��Ҳ�����γɷ��Ͳ���Ҫ���ܵ������

ע�ۣ���ͨ/�Ͽ��ӳ�ʱ��t d(on/off)������/�½�ʱ��tr / tf����λ����ʱʹ�õ�ʱ�������ʵ��©����·ID��դ��������ѹVg�����жϡ�

MOS�Ľ��ܻ������ϣ�ʱ�估ƪ����ϵ���в��漰�����·���⡣ͼԴ����Ҫ�ο��鼮Ϊ��ģ����Ӽ�������,(ͯʫ��.��4��)���������Ӽ�������.ģ�ⲿ��.(������.��5��)������λ����ʦ����ʱ����ѧ�α���ʱ���в�ͬ���ջ�

���ض���

���ض��� ˢ��ҳ��

ˢ��ҳ�� �µ�ҳ��

�µ�ҳ��