оƬһ����ָ���ɵ�·�����壬Ҳ�Ǽ��ɵ�·������ơ����졢��װ�����Ժ�Ľ����ͨ����һ����������ʹ�õĶ��������塣��������봦����CPU����Ϊ��������ϵͳ�����࣬��ô�����ϵ�оƬ�����������������ɡ�����������ԣ�оƬ�鼸���������������Ĺ��ܣ�����Ӱ�쵽��������ϵͳ���ܵķ��ӣ�оƬ�����������ꡣ

��ôҪ�����оƬ�����ȣ���û�����һ�����������������Foundry (����ľ�Բ���칫˾)��

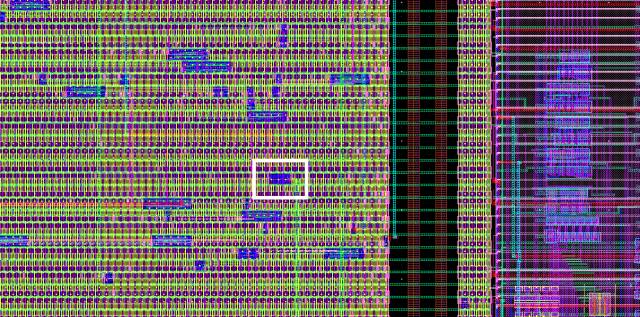

�ٷŴ�

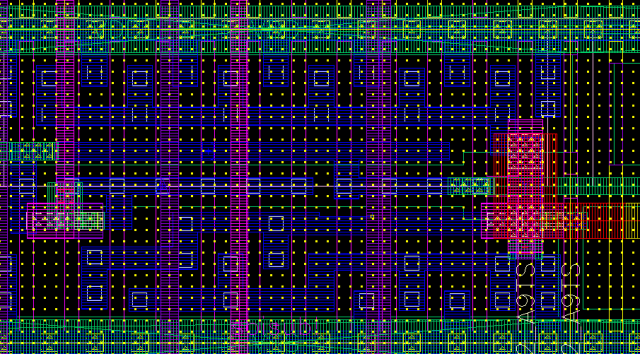

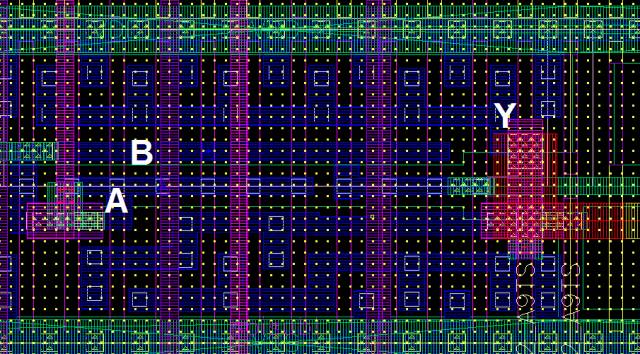

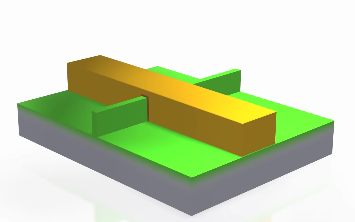

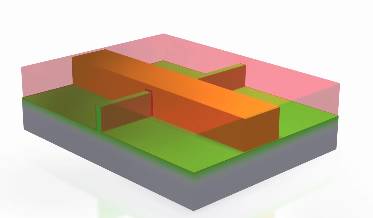

�������ڿ���һ���ŵ�·��! ����һ��NAND Gate(�����)�������������

A, B ������, Y�����

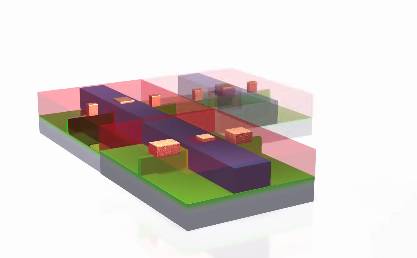

������ɫ���ǽ���1�㣬��ɫ�ǽ���2�㣬��ɫ�ǽ���3�㣬��ɫ�ǽ���4�㡣�Ǿ����(������ܡ���199X���Ժ��Ѿ���Ҫ�� MOSFET, ����ЧӦ���� ) �أ���ϸ��ͼ������������Щ��ɫ�ĵ������dzĵף�����һЩ��ɫ�ı߿���Щ��Active Layer (Ҳ�����Ӳ�)��

Foundry����ô������? �����Ϸ�Ϊ���¼���:

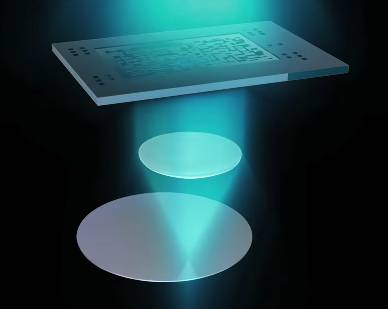

���ȸ㵽һ��ԲԲ�Ĺ辧Բ, (����һ��龧���, ��ĥ�ĺܹ⻬, һ����Բ��)

ͼƬ����������������. ���Dz����ܽᵥ��д��.

1��ʪϴ(�ø����Լ����ֹ辧Բ����û������)

2�����(�����������ɰ�����辧Բ, ���յ��ĵط��ͻ����ױ�ϴ��, û���յ��ĵط��ͱ���ԭ��. ���ǾͿ����ڹ辧Բ����̳���Ҫ��ͼ��. ע��, ��ʱ��û�м�������, ��Ȼ��һ���辧Բ. )

3�� ����ע��(�ڹ辧Բ��ͬ��λ�ü��벻ͬ������, ��ͬ���ʸ���Ũ��/λ�õIJ�ͬ������˳�ЧӦ��.)

4.1����ʴ��(֮ǰ�ù�̳�������״��������ʵ����������Ҫ�ģ�����Ϊ������ע���ʴ�̵ġ����ھ�Ҫ�õ������������ϴ����������һЩ��һ������Ȳ���Ҫ�̳����Ľṹ����һ������ʴ��).

4.2��ʪʴ��(��һ��ϴ���������õ����Լ��� ���Խ�ʪʴ��)���� ���ϲ�����ɺ�, ��ЧӦ�ܾ��Ѿ��������������������ϲ���һ�㶼��ֹ��һ��, �ܿ�����Ҫ���������������ԴﵽҪ��

5�������ӳ�ϴ(�ý����ĵ��������������оƬ)

6���ȴ����������ַ�Ϊ��

6.1 �������˻� (����˲�������Ƭ��ͨ�����ʵ�ɶ���յ�1200���϶�����, Ȼ����������ȴ����, Ϊ��ʹ��ע��������ܸ��õı������Լ�������)

6.2 �˻�

6.3 ������ (�������������, Ҳ����ЧӦ�ܵ�դ��(gate) )

7����ѧ�������(CVD)����һ����ϸ��������ĸ�������

8������������� (PVD)�����ƣ����ҿ��Ը����в�����coating

9������������ (MBE) �����Ҫ�������Ļ�����Ҫ��

10����ƴ���

11����ѧ/��е���洦��

12����Բ����

13����Բ��ĥ�Ϳ��Գ�����װ�ˡ�

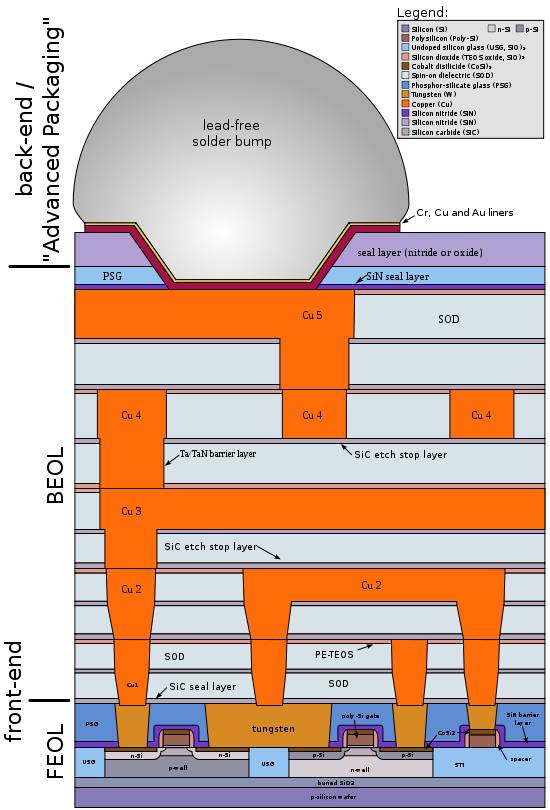

��ͨ��ͼʾ��һ��������

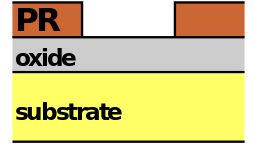

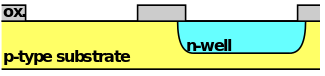

1��������������, �����dzĵ�(��)����ʪϴ

2��һ����˵, �ȶ������ĵ�ע������(10^10 ~ 10^13 / cm^3) ��P������(�������һ������)����Ϊ�ĵס�������ע��

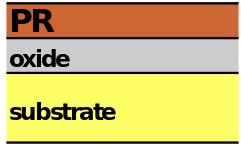

3���ȼ���Photo-resist, ����ס���뱻ʴ�̵ĵط��������

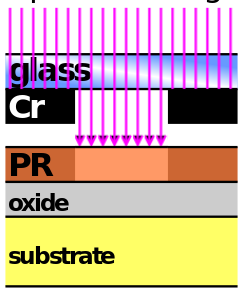

4������Ĥ�� (�����Ǹ���עCr�ĵط����м�յı�ʾû���ڸǣ��ڵı�ʾ��ס�ˡ�) ���� ���

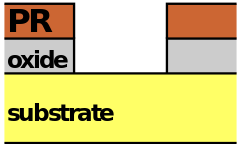

5������������ȥ�����汻�յ���һ��ͱ���Ӧ�ˡ������

6����ȥ��Ĥ�������

7���ѱ�¶������������ϴ��, ¶�����(�Ϳ���ע��������)�������

8���ѱ����㳷ȥ. �����͵õ���һ����ע��Ĺ�Ƭ. ��һ���ᷴ���ڹ�Ƭ�Ͻ���(��ʮ�������ϰٴ�)�������

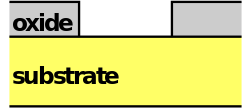

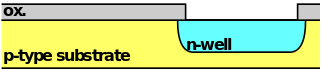

9��Ȼ������Ϻ�, ������ݺݵز���һ������(10^14 ~ 10^16 /cm^3) ע���N�����ʾ�������һ��N-well (N-��)��������ע��

10���ø�ʴ�̰���ҪP-well�ĵط�Ҳʴ�̳�����Ҳ�����ٴ�ʹ�ù�̳̿���������ʴ��

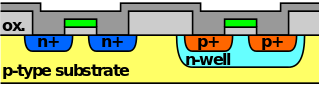

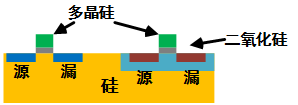

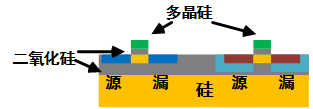

11����ͼ��P-�Ͱ뵼���ϲ��ٴ�������һ�㱡���Ķ������衪�� �ȴ���

12���÷��������Ӵ���������һ��ྦྷ�裬�ò�ɵ��硪������������

13����һ����ʴ�̣�������ϸ�Ľṹ��(���˻��Լ�����CVD)���� �ظ�3-8��� + ʪʴ��

14���ٴκݺݵز������(10^18 ~ 10^20 / cm^3) ע���P/N�����ʣ���ʱע��MOSFET�Ѿ��������͡�������ע��

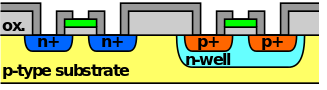

15����������� �γɵĵ������ ���� ��ѧ�������

16����������ʴ�̳������������ + ʪʴ��

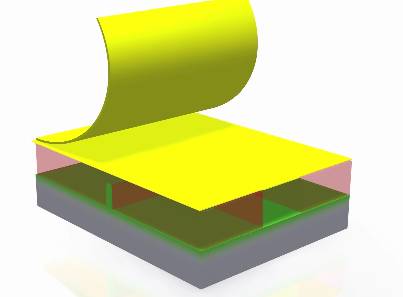

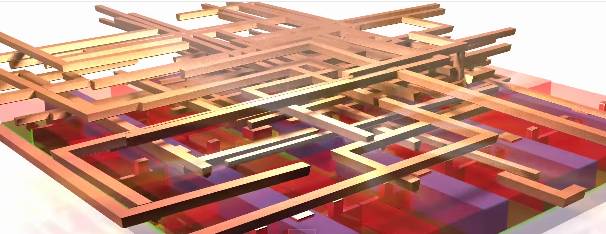

17����������������� �����㡪�������������

18�������������ʴ�̡���� + ʪʴ���ظ� 17-18 �γ���ÿ�������㡣

��ͼ�IJ�����ÿ��ͼ�������ע��һ��18����

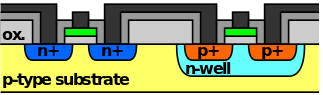

���ճ��ʹ�ų�����:

���У�����1-15 ���� ǰ�˴��� (FEOL)��Ҳ�����������ЧӦ�ܡ�����16-18 (�������������ظ�) ���ں�˴��� (BEOL)����˴�����Ҫ���������ߡ��ʼ�Ǹ���оƬ�����ܿ����Ļ������Dz��ߣ�һ��һ���߶ȼ��е�оƬ�ϼ����������ײ�Ĺ�Ƭ�����ᱻ�����ڵ�ס��

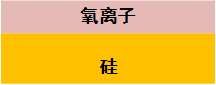

SOI (Silicon-on-Insulator) ������

��ͳCMOS������ȱ�����ڣ��ĵĺ�Ȼ�Ӱ��Ƭ�ϵļ������ݣ���ӵ���оƬ�������½��� SOI������Ҫ�ǽ� Դ��/©�� �� ��Ƭ�ĵֿ����Դﵽ(����)�����������ݵ�Ŀ�ġ�

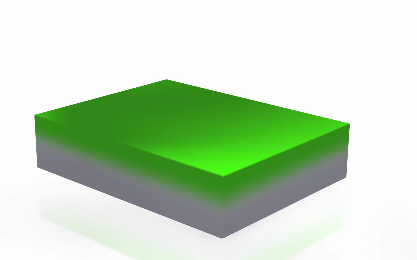

��ͳ��

SOI:

����������Ҫ�����¼���(��Ҫ����������-��������-��Ľṹ��֮��IJ������ͳ���ջ���һ�¡�)

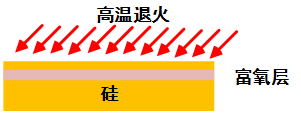

1. ���������˻�:

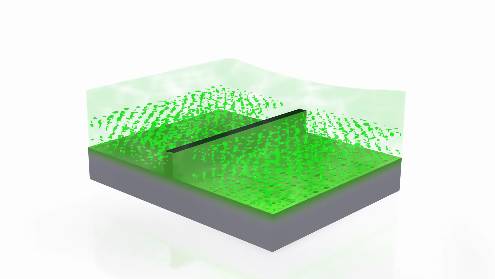

�ڹ��������ע��һ�������Ӳ�

��������������, �γɸ�����

�����˻�

����

������

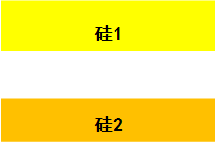

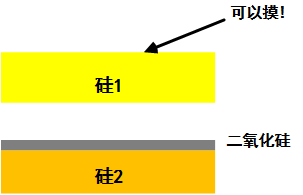

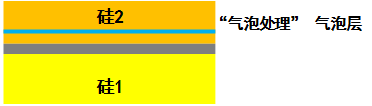

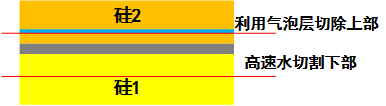

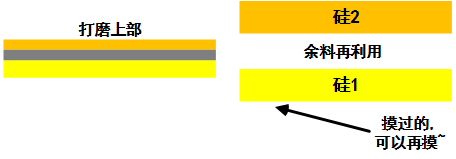

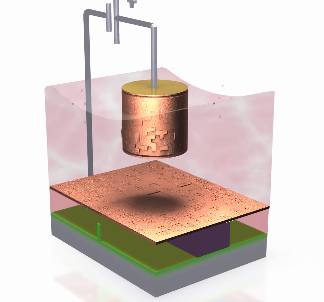

2. Wafer Bonding(������! )����Ҫ�����ı���һ���Ľṹ��? ү����Ǯ! ������!

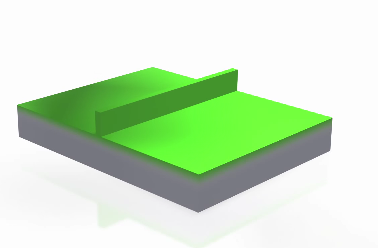

�Թ�2���б�������

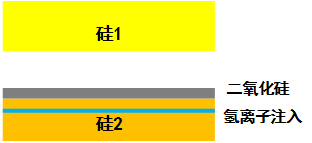

�Թ�2����������ע��Թ�2����������ע��

����

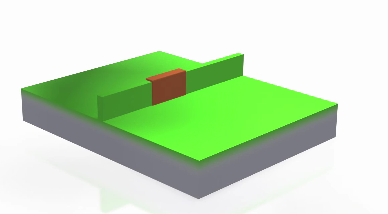

�������Ӳ㴦�������ݲ㽫�����Ӳ㴦�������ݲ�

�и�����ಿ���и�����ಿ��

���� + ������

���

����ע������ע��

��ͼ������:

�ٴι��+ʴ��

��ȥ����, �м��Ǹ�����Fin��ȥ����, �м��Ǹ�����Fin

�Ų�λ�Ķྦྷ��/��K���������Ų�λ�Ķྦྷ��/��K��������

�Ų�λ�������������Ų�λ������������

��������

Դ�� ©������(���+ ����ע��)

�������/�ྦྷ����Ƭ

ʴ��+����

������������������������(��Ϊ����ά�ṹ, ��������Ҫ���ϲ�����)

��е��ĥ(��! ����ĥ�ᵼ�½������Ȳ�һ��)

����! ����!

���ض���

���ض��� ˢ��ҳ��

ˢ��ҳ�� �µ�ҳ��

�µ�ҳ��